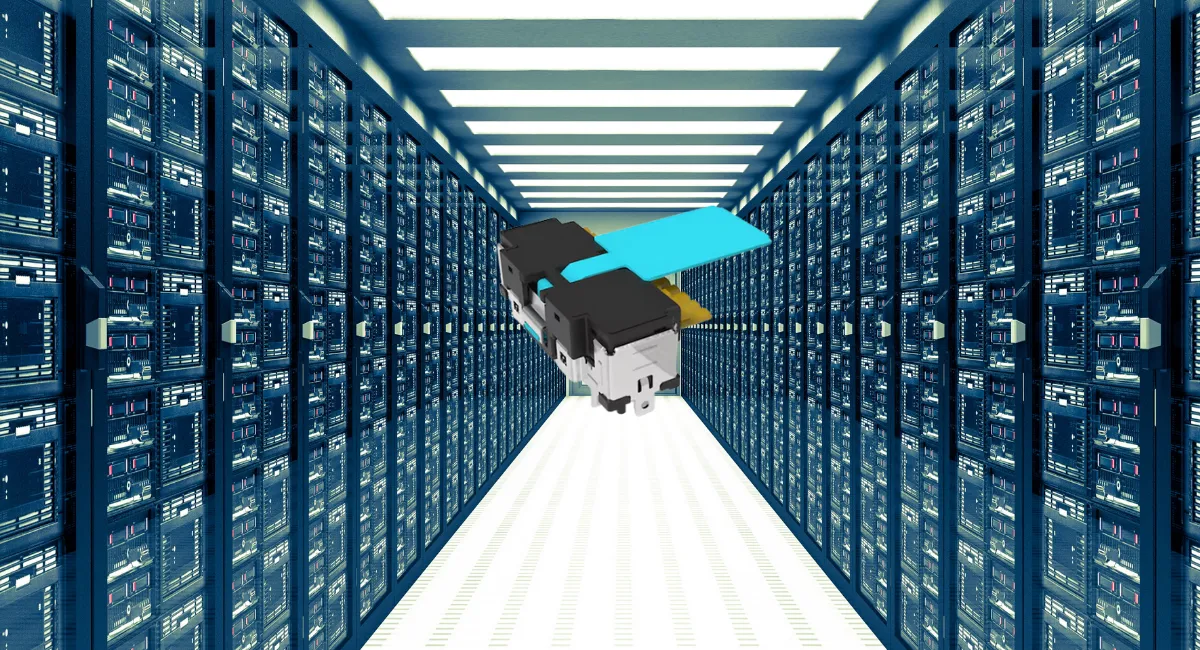

TE Connectivity Launches Ultra Low-Profile PCIe Gen 7 Connectors for AI and Data Centers

AI infrastructure is evolving faster than many hardware standards can keep pace with. Training models with trillions of parameters requires throughput far beyond what PCIe Gen 5 or even Gen 6 comfortably deliver. PCIe Gen 7, with its 128 GT/s data rate, is the next step. But as system speeds rise, so do the practical design constraints: dense layouts, oversized heatsinks, and limited clearance make it harder to integrate high-speed connectors where they are needed most.

AI infrastructure is evolving faster than many hardware standards can keep pace with. Training models with trillions of parameters requires throughput far beyond what PCIe Gen 5 or even Gen 6 comfortably deliver. PCIe Gen 7, with its 128 GT/s data rate, is the next step. But as system speeds rise, so do the practical design constraints: dense layouts, oversized heatsinks, and limited clearance make it harder to integrate high-speed connectors where they are needed most.

TE’s Ultra Low-Profile Approach

This is the context behind TE Connectivity’s release of its Ultra Low-Profile (ULP) PCIe Gen 7 connectors and cable assemblies. Demonstrated earlier this year at DesignCon 2025, the connectors are built to combine Gen 7 bandwidth with a mating height of just 8.7 mm.

The low profile allows placement in locations that are often blocked in current designs, beside CEM slots, underneath cooling hardware, or next to processors. For engineers, this matters because it opens up routing options in boards where every millimetre of clearance has to be negotiated.

Design Characteristics

The ULP family is designed with signal integrity in mind. Centrally located sidebands are used to improve host board routability, helping maintain cleaner paths in dense layouts. This feature addresses one of the major difficulties of moving from Gen 6 to Gen 7: keeping crosstalk and reflections low enough to sustain stable channels at higher speeds.

TE plans to offer x4, x8, and x16 configurations, giving designers the ability to apply the same interconnect approach across accelerators, storage, and networking modules. Samples are already being provided to select customers, with volume production expected in early 2026.

Practical Engineering Impact

In hyperscale and AI-focused data centres, the limiting factors are no longer just clock speeds or memory bandwidth. Layout and thermal challenges often dictate what is possible. Large GPUs and dedicated accelerators occupy more board area than ever, while advanced cooling systems take up vertical space that used to be available for interconnects.

An 8.7 mm profile may seem like a small change, but it enables connectors to be placed where they previously could not. That flexibility reduces the risk of mechanical conflicts and gives engineers new options for airflow management. Combined with improved routability, it can shorten the path to achieving Gen 7 performance without extensive board re-spins.

Broader Applications

Although clearly aimed at data centres and AI infrastructure, the same requirements exist in other sectors. Edge servers, high-performance workstations, and compact accelerator platforms all face similar constraints. By enabling high-speed links in restricted spaces, the ULP PCIe Gen 7 family could broaden adoption of the new standard beyond hyperscale environments.

Conclusion

Moving to PCIe Gen 7 is not just about increasing data rates. For many engineers, the bigger challenge is making the physical design practical at scale. TE Connectivity’s Ultra Low-Profile connectors reflect this shift, addressing the realities of board density, thermal design, and routability as much as raw throughput. With samples available now and production scheduled for 2026, the new connectors will likely be part of the next wave of AI-focused system designs.

Learn more and read the original article on www.te.com