Synopsys has broadened its Synopsys.ai platform with new generative AI features, aiming to speed up chip design workflows and reduce some of the bottlenecks engineers face in verification, coding, and simulation. The updates arrive as design teams contend with soaring complexity in advanced SoCs and a shortage of experienced engineers.

Synopsys has broadened its Synopsys.ai platform with new generative AI features, aiming to speed up chip design workflows and reduce some of the bottlenecks engineers face in verification, coding, and simulation. The updates arrive as design teams contend with soaring complexity in advanced SoCs and a shortage of experienced engineers.

Assistive AI To Shorten Ramp-Up

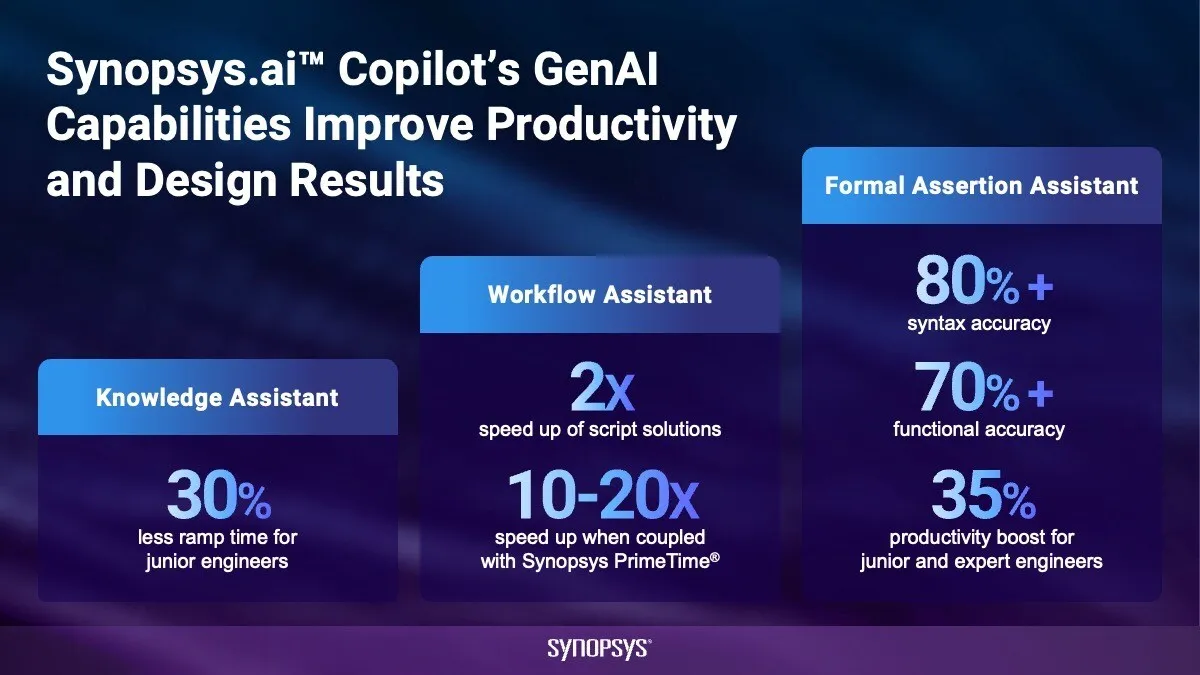

One of the more practical uses of AI in EDA is simply helping engineers find their footing faster. Synopsys is rolling out new knowledge and workflow assistants that slot directly into its tools. These assistants handle tasks like documentation searches and script generation, jobs that can easily eat up hours. Early users report ramp-up times for junior engineers cut by nearly a third, with script generation in PrimeTime running ten to twenty times faster than traditional approaches.

The value here is not just speed. By lowering the entry barrier, Synopsys is making it easier for less experienced engineers to work independently while keeping quality consistent. For large teams balancing seasoned specialists with new hires, that independence could matter as much as the time saved.

Creative AI In Verification And RTL

On the creative side, Synopsys is testing GenAI for assertion generation and RTL code creation. Formal verification in particular has been a time sink, but early adopters say automated testbench creation is shortening cycles from days to hours. One AI infrastructure company validated ten design components in ten days, reporting a 35% jump in productivity across both new and senior engineers.

Extending AI Into Simulation

Following the integration of Ansys earlier this year, Synopsys is also weaving AI into multiphysics simulation. The new Ansys Engineering Copilot works as a virtual assistant inside Synopsys tools, helping engineers cut learning curves and set up runs more quickly. Meanwhile, Ansys SimAI, now tied into optiSLang, is being positioned as a way to generate datasets faster and accelerate AI training for design variation studies.

Looking Toward Agentic AI

Longer term, Synopsys is exploring what it calls AgentEngineer, a multi-agent AI system developed with Microsoft. The idea is to progress from step-level automation to more adaptive, flow-level optimisation, and eventually to systems that can make design choices on their own. The first prototype was shown at DAC 2025, and while still at an early stage, Synopsys suggests it could change how much of the chip design process requires direct human oversight.

To learn more, visit www.synopsys.com