High-speed links do not usually fail because the clock disappears. They fail because timing drifts just enough for the margin to get eaten away a little at a time. At lower data rates, that can stay hidden for a while. In AI servers, optical modules, and faster network hardware, it gets harder to ignore. Jitter that once looked acceptable starts showing up as a system problem instead of a spec-sheet detail, especially when the links are dense and the noise environment is not forgiving.

High-speed links do not usually fail because the clock disappears. They fail because timing drifts just enough for the margin to get eaten away a little at a time. At lower data rates, that can stay hidden for a while. In AI servers, optical modules, and faster network hardware, it gets harder to ignore. Jitter that once looked acceptable starts showing up as a system problem instead of a spec-sheet detail, especially when the links are dense and the noise environment is not forgiving.

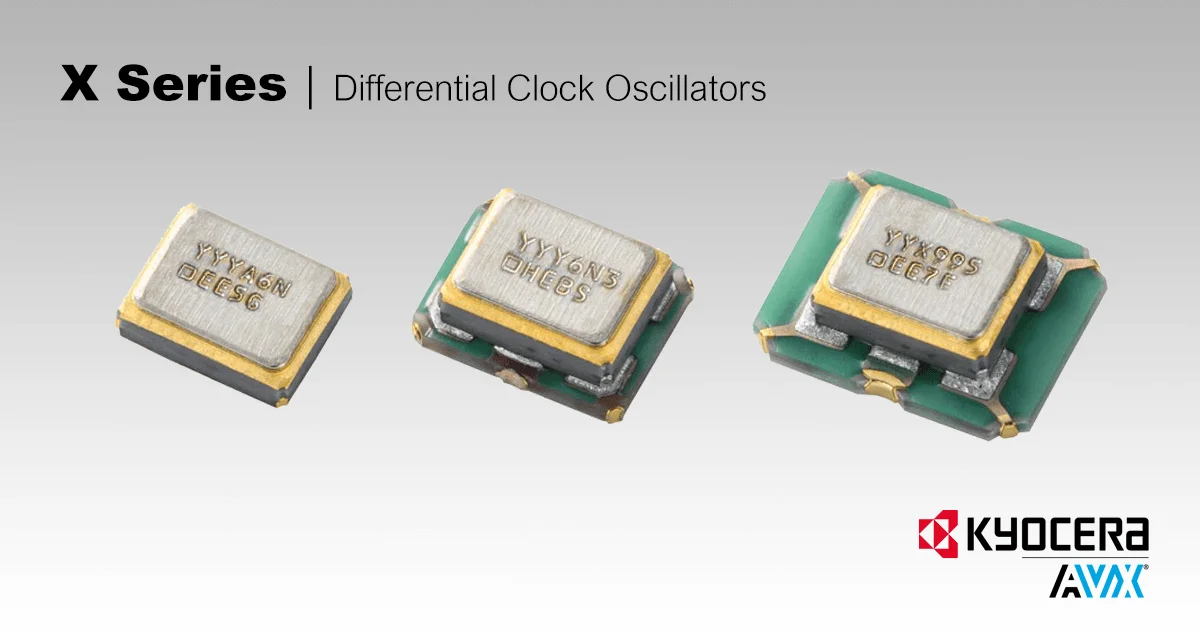

Kyocera is aiming its new X Series squarely at that problem. The X Series is a family of differential clock crystal oscillators used to provide low-jitter reference timing for high-speed data communication systems such as AI servers, optical transceivers, storage equipment, and automotive ADAS hardware. In a typical AI server or network system, a device like this provides the clock reference that downstream serializers, transceivers, and processing hardware depend on to keep data aligned at speed.

The central claim here is phase jitter. Kyocera says the X Series reaches 30 fs typical jitter, with 40 fs at 156.25 MHz and 30 fs at 312.5 MHz. That is the part that makes the release interesting. Differential oscillators already have a place in noisy high-speed systems because they reject common-mode interference better than single-ended clocks. What changes here is how far the clock itself is being pushed as a noise and timing bottleneck in AI infrastructure.

Differential Outputs Matter More Once Timing Margin Tightens

Single-ended oscillators are still common in a lot of standard electronics, but they are not really where the pressure is building. Once links get faster and channel budgets get tighter, differential clocking becomes more attractive because the receiver is evaluating the difference between two signals rather than relying on one line trying to stay clean on its own.

That is why Kyocera is leaning on the AI server and 5G infrastructure angle. In high-speed communication, small timing errors and added noise can turn into bit errors quickly, and that puts more weight on the reference clock than people sometimes admit. The X Series supports LV-PECL and LVDS outputs, with frequency options of 100 MHz, 125 MHz, 156.25 MHz, and 312.5 MHz. Those are familiar clock points for data communications hardware, which makes the series easier to place in real designs rather than as a niche timing part.

The package options are also compact, spanning 2.0 x 1.6 x 0.5 mm, 2.5 x 2.0 x 0.5 mm, and 3.2 x 2.5 x 0.5 mm. That matters because clock devices tend to end up near already crowded signal paths where board space does not improve simply because timing is important.

Lower Power Starts Mattering When The Clocks Multiply

The other useful part of this launch is power consumption. One clock source is rarely the thing that breaks a server power budget, but large systems are built from a lot of small line items that do not stay small in aggregate. Kyocera says the X Series reduces power by about 42 percent compared with conventional products in the 156.25 MHz LV-PECL configuration, dropping to 29 mA from a typical 50 mA.

At 156.25 MHz, the company lists 29 mA for LV-PECL output and 14 mA for LVDS. At 312.5 MHz, that rises to 45 mA for LV-PECL and 23 mA for LVDS. Those are not spectacular numbers in isolation, but in hardware where timing devices are replicated across multiple channels, boards, and modules, lower current starts becoming part of the thermal and efficiency story whether anyone planned for it or not.

Kyocera also says the 30 fs figure represents about a 25 percent reduction in phase jitter versus conventional products at the same frequency. That is exactly the sort of improvement that matters most in systems where the clock is not allowed to be the quiet source of avoidable margin loss.

AI Infrastructure Is Pushing Timing Parts Harder Too

A lot of AI infrastructure discussion stays focused on processors, optics, and power conversion, which is understandable, but it misses how many supporting components are also being pushed harder. Timing is one of them. Faster links, longer paths, and denser data movement make the reference clock more exposed than it used to be.

That is where the X Series fits. Not as a glamorous part of the system, but as one of the pieces that has to get quieter while using less power and fitting into smaller spaces. In high-speed hardware, the clock does not need much attention when it is working. It gets everyone’s attention once it is not.

Learn more and read the original announcement at www.kyocera.com

Technology Overview

The X Series is a family of differential clock crystal oscillators for high-speed data communication systems. It supports LV-PECL and LVDS outputs, frequencies from 100 MHz to 312.5 MHz, and supply voltages of 1.8 V, 2.5 V, or 3.3 V, with typical phase jitter as low as 30 fs. The oscillators are intended for applications including AI servers, optical transceivers, storage systems, and automotive ADAS equipment.

Frequently Asked Questions

What is the Kyocera X Series used for?

It is used as a low-jitter differential clock source in AI servers, optical transceivers, storage applications, and automotive ADAS equipment.

What output types does the X Series support?

Kyocera lists LV-PECL and LVDS output options.