Running MOSFETs in parallel is common practice in high-power designs. The idea is simple: spread current across multiple devices, cut conduction losses, and handle more load. The reality is harder.

Running MOSFETs in parallel is common practice in high-power designs. The idea is simple: spread current across multiple devices, cut conduction losses, and handle more load. The reality is harder.

Each MOSFET has a slightly different threshold voltage. The one with the lowest value switches on first, pulling more current than its neighbours. That device heats up faster, carries more stress, and often fails sooner. Instead of sharing the load evenly, the system ends up unbalanced.

Designers usually cope by oversizing the MOSFETs or ordering matched sets. Both options add cost, time, and uncertainty. Neither guarantees smooth behaviour once current climbs into the tens of amps.

A Different Path

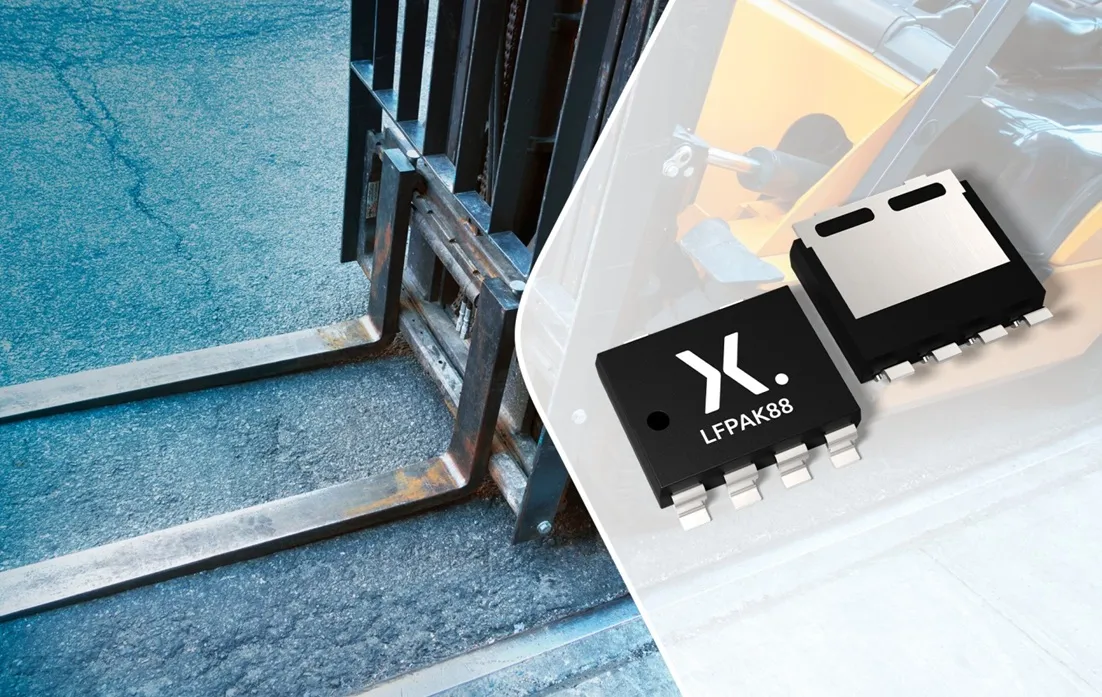

Nexperia has released two application-specific MOSFETs designed to solve this problem directly. The 80 V PSMN1R9-80SSJ and the 100 V PSMN2R3-100SSJ are tuned for better dynamic current sharing when multiple devices are used in parallel.

In testing, these ASFETs cut the current imbalance between parallel devices by about 50 percent during turn-on and turn-off. They also narrow the threshold voltage spread to just 0.6 V from minimum to maximum, around half the variation seen in typical devices. For engineers, that means less guesswork when designing high-current stages.

What the Specs Say

Alongside current sharing improvements, the devices bring low conduction losses. The PSMN1R9-80SSJ offers 1.9 mΩ RDS(on) while the PSMN2R3-100SSJ comes in at 2.3 mΩ. These values keep switching efficient while reducing wasted heat.

Both arrive in the LFPAK88 package. It measures 8 mm by 8 mm and uses a copper-clip design to spread heat effectively. Operating range is -55 °C to +175 °C, so the devices are prepared for demanding industrial or mobility environments.

Where They Fit

The obvious target is 48 V systems. That includes industrial motors, robotics, and mobility platforms such as forklifts, scooters, and medical transport devices. These are applications where parallel MOSFET use is routine, but overspecification has long been the default approach.

By improving current balance at the silicon level, Nexperia removes the need for that extra safety margin. Engineers can design around standard devices, avoid the cost of tightly matched sets, and still have confidence in long-term reliability.

What It Means for Design

For engineers, the value here is predictability. Instead of designing with wide margins to protect against device mismatch, the circuit behaves more consistently. Startup events are easier to manage. Load transients are less likely to stress one device disproportionately.

The result is a parallel MOSFET stage that requires fewer workarounds and delivers higher efficiency. That translates into smaller systems, lower costs, and less time spent chasing thermal issues downstream.

A Subtle but Useful Step

On the surface, the new ASFETs look like incremental improvements. In practice, they take one of the persistent headaches of high-power design, uneven current sharing, and deal with it at the source. That makes life easier for designers and supports the move toward more compact, efficient 48 V systems in both industrial and mobility applications.

Learn more and read the original article on www.nexperia.com